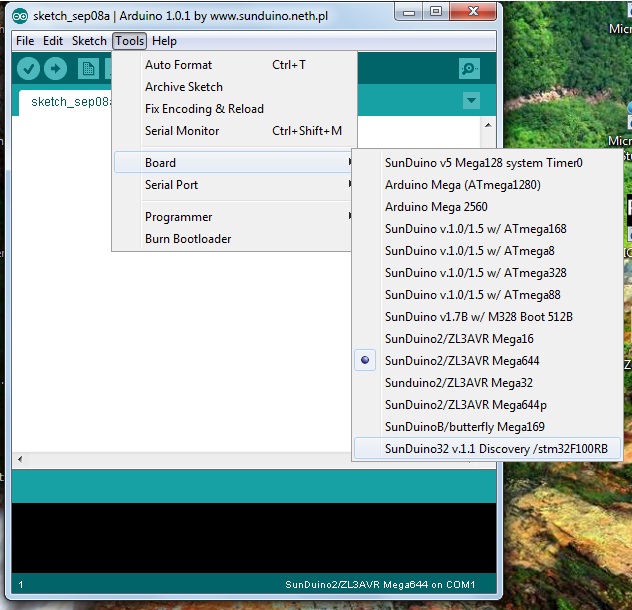

Mój algorytm przeznaczony jest w zasadzie dla FPGA, choć 100Mhz Arm Cortex daje radę generować sygnały step do około 100kHz ( dla 4 osi).

Źródłem przerwań jest chodzący synchronicznie zegar( 10us) i przeliczający za każdym krokiem każdą oś. Kilka dodawań stałoprzecinkowych liczb 64 bitowych i jest

Poszło by szybciej gdyby napisać w assemblerze, ale na razie 100kHz mi wystarcza. W tej chwili testuję ARMa 120Mhz ( LPC1788 + SDRAM) + sieć ( uIP z UDP ) i też wyciąga 100kHz.

Wiem ze nie jest to idealne, można by robić jak MACH - odcinkami o stałej prędkości - wtedy dało by radę używać do 'stepów' timerów sprzętowych.